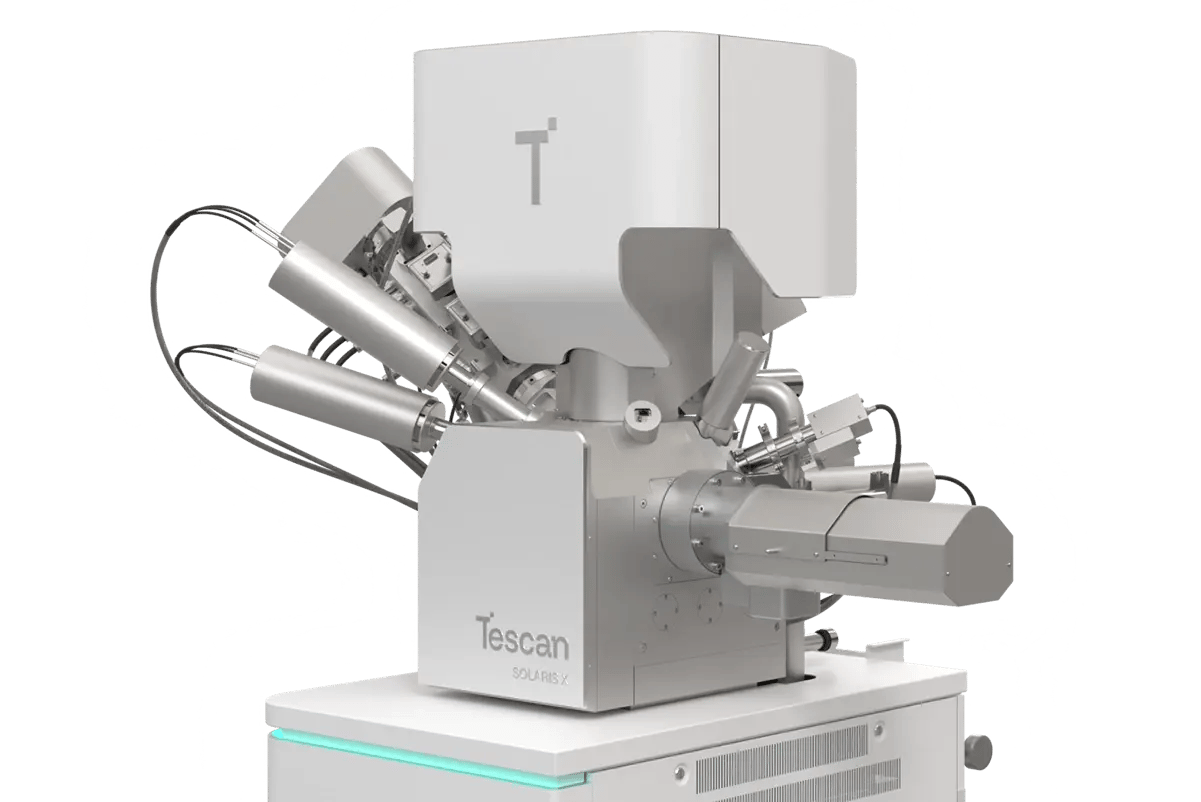

Combine gas-assisted delayering with inverted geometry and precise endpoint control to prepare sub-20 nm TEM lamella from 7 nm devices. This integrated workflow preserves structural integrity and delivers reliable high-resolution analysis.

- Nanoflat chemistry: Maintains planarity and contrast across complex multilayer stacks

- Inverted geometry: Improves lamella stability, reduces curtaining, and enables precise thinning

- Real-time inspection: Preserves delicate transistor and contact features for accurate TEM imaging