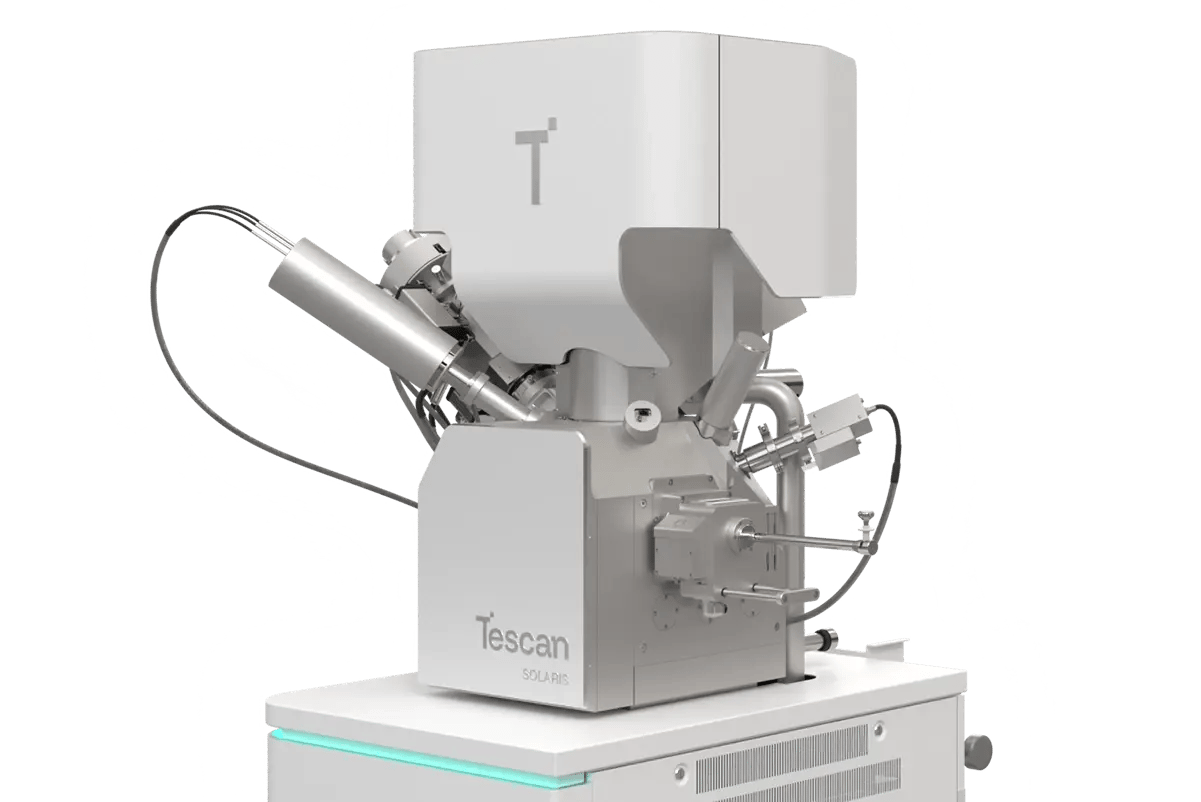

TESCAN SOLARIS 2 FIB-SEM

Tescan SOLARIS 2 FIB-SEM delivers the precision, stability, and imaging performance required for advanced TEM lamella workflows on 10 nm FinFET devices.

It integrates high-resolution SEM imaging with controlled Ga FIB milling, enabling site-specific preparation of sub-10 nm samples without compromising structure.

You can prepare both gate-cut and fin-cut lamella with confidence, using in-situ lift-out, inverted geometry, and low-keV thinning to achieve optimal quality and consistency.

- Integrated SEM and Ga FIB platform: supports full trenching, lift-out, and thinning workflows on a single system

- In-situ lift-out capabilities: minimize contamination and reduce handling risks during TEM sample transfer

- Sub-10 nm lamella preparation: ensures dimensional accuracy for high-resolution TEM analysis

- Optimized workflow stability: allows for reproducible sample prep across FinFET devices

- Application-tuned system control: supports inverted geometry and precise polishing routines