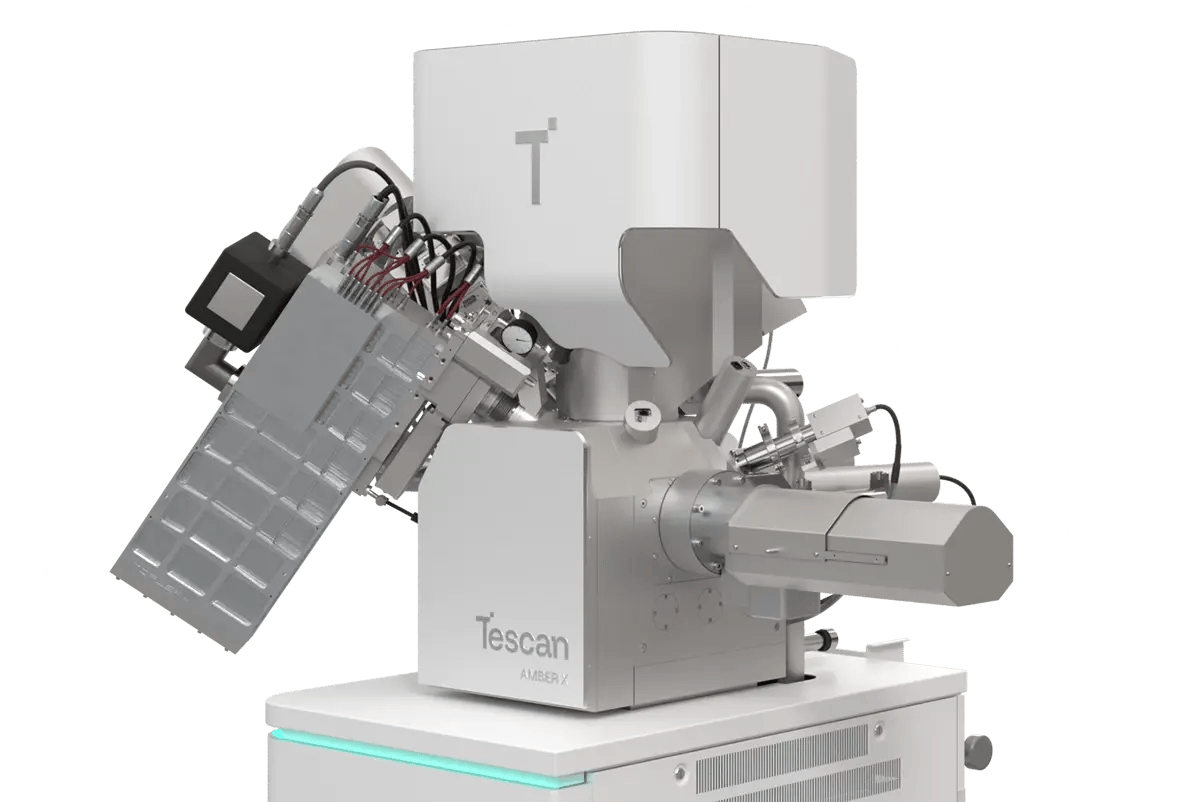

Tescan AMBER X™ 2 – Plasma FIB-SEM

A unique plasma FIB-SEM combining a Xenon plasma FIB with a field-free UHR SEM column, enabling high-throughput milling and high-resolution imaging. Tescan AMBER™ X 2 is ideal for delayering including thick I/O regions and upper interconnect stacks, delivering curtaining-free surfaces that preserve device structures for further analysis.

- Xenon plasma FIB: ensures efficient, large-area material removal

- Ultra-high-resolution SEM imaging: verifies surface quality during delayering

- Field-free design: allows precise imaging of delicate structures without distortion